半導体・通信の発展の概要 後編

平野拓一

(東京都市大学 理工学部 電気電子通信工学科・准教授)

平野拓一

(東京都市大学 理工学部 電気電子通信工学科・准教授)

– 専門 –

電磁界理論(モーメント法 [MoM; Method of Moments]、 有限要素法

[FEM; Finite Element Method]、FDTD法, ICT [Improved Circuit Theory])

アンテナ工学

情報通信工学

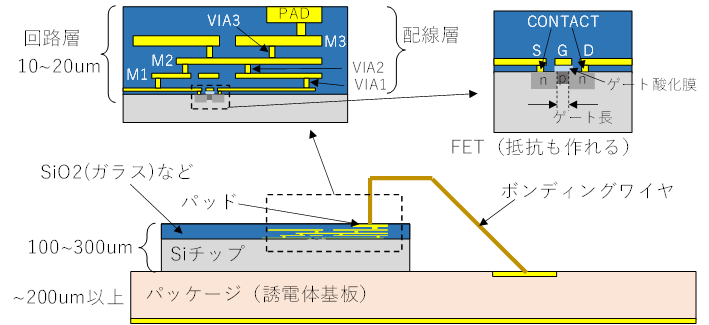

半導体のメインの回路素子はFET(電界効果トランジスタ)であり、どの程度小さなFETを作れるかという指標は技術ノード(プロセスノード、技術世代、プロセス世代)と呼ばれます。

例えば、180nmのプロセス世代と言ったら、トランジスタのゲート長(下図)が大体180nm程度ということを意味します(正確には180nmがゲート長を表すのかどうかは、各社定義が曖昧なようで、STI (Shallow Trench Isolation)間隔を基準にしたりすることもあるようです)。180nmの次のプロセス世代は何nmかというと、集積度2倍、つまり同じ面積に2倍のトランジスタが詰め込まれているので、トランジスタの面積は1/2なので、長さの次元のゲート長は1/√2で180/√2≒130nmとなります。このように、次々に1/√2倍して90nm、65nm、45nm、32nm、22nm、14nm、10nm、7nm、5nm・・・と微細化が続いています。このように、次の目標はしっかり集積度2倍に設定されているのがわかります。

半導体関係の企業が合同で作った組織が技術の将来予測を公開しているものがロードマップ[7][8]です。

初期の頃はムーアの法則はかなり信頼性の高い予測ができました。例えば、ゲーム機の映像は販売された時代の最先端でなければ売れないので、プレイステーション2用の画像処理プロセッサEmotion Engineの開発では、現在はまだないが将来の生産時には開発されるであろうプロセスで作ることを想定して回路設計していたことが[9]の記事にも書かれています。また、Pixarの歴史について書いた記事[10]には”Then, at last, Moore’s Law saved us. The ever-falling cost of processing power finally made The Movie economically feasible.”とあります。

当初は比較的簡単であった微細化も、原子のサイズが無視できない大きさになってくることから途中からは一筋縄ではいかなくなります(それでも、まだ微細化が続いて、本当に原子数個レベルの制御ができるようになっていることは驚愕です)。

例えば、65nmから45nmのプロセスに移行するときは、ゲート電極の絶縁体として使われるSiO2(ガラス)のゲート酸化膜(下図)は厚さが1.2nm(5原子程度)になってしまい、リーク電流が大きな課題となっていたそうで、その問題を乗り越える苦労が[11]に書かれています。また、25nm程度よりもゲート長が小さくなった場合には平面型トランジスタではなく、3次元構造のトランジスタFinFETが使われます[12][13][14]。さらに微細化が進むと積層ナノシートトランジスタ[15]が考案されています。

ところで、半導体ではFETが主役ですが、トランジスタ同士の配線もまた高い集積度です。

配線層はシリコン(Si)の表面の上に形成されており、多段になっています。プロセス世代が進むごとに配線層の数も増えて、現在では10層以上となっています(例えば、[14]や[16]を参照してください)。

一般に、上の層ほど厚い配線になっています。1層あたりの厚さは1umあるかないかです。多層配線層を形成するには1層ずつ積み上げていくわけですが、その際に各層の平坦度は高い精度が要求され、CMP(Chemical Mechanical Polishing; 化学機械研磨)行程が入ります。

液剤を塗って平坦に研磨する工程で、この際に金属よりもSiO2の方が柔らかく凹んでしまい、後工程に影響を及ぼします。そのため、金属は各層に一定の面積割合を均一に入れないとならないという規則があり、ダミーメタルという小さな面積の金属が多数入ることになります。このような製造上の問題を無くすための規則をデザインルールと言います。

シリコンチップの厚さ(ウェハ―の厚さ)は通常300um(0.3mm)程度ですが、トランジスタと配線層を合わせた厚さはその表面の10-20um程度と非常に薄いです。また、微細化されることで動作周波数を上げることができますが、そすると数mm角のチップ内の配線による信号の遅延も無視できなくなってきます。このため、従来は比誘電率4のSiO2(ガラス)が配線間の絶縁体として使われていましたが、より誘電率の低い材料が一部に用いられたり、一部に空気を入れたり[17]しています。

チップ内の微細化は原子サイズが見えてきているからもう不可能だ・・・と言われ続けていますが、様々なブレイクスルーにより微細化が続いてます。チップ内の集積化向上とともに、チップを積層した集積化技術も進みました。TSV(Through-Silicon Via)[18]と呼ばれるもので、チップを非常に薄く削り、ビア(穴を空けて金属で電気的に接続する)を使って複数のチップを積層する技術です。近年、スマートフォンの普及とともに磁気記録のハードディスクドライブ(HDD)が大容量NANDフラッシュメモリのSSD (Solid State Drive)に置き換わっていますが、SSDの大容量化にはTSVの技術が欠かせません。チップを薄く削る技術はCMOSイメージセンサの感度向上にも寄与しています(裏面照射型CMOSセンサー)。従来は回路がある表面から光を照射していましたが、配線層の金属の影響で光が減衰してしまいます。そのため、裏面から光を入れればいいのですが、その代わりに薄く削る必要があるわけです。

高度なグラフィック処理が要求されるようになり、3Dグラフィックス専用のプロセッサであるGPU (Graphics Processing Unit)が登場しました。また、この並列演算はグラフィックのみならず、GPGPUとして汎用計算にも使われるようになりました。今は深層学習の応用が盛んになり、ますますGPGPUが使われるようになっています。

NVIDIA等に代表されるような半導体製造工場をもたず、回路設計のみを行う企業(ファブレスカンパニー)が登場し、さらに回路設計(マスクパターン)を元に製造のみを行うファウンドリー(ファブ)の分業が起こりました。

代表的なファウンドリーは台湾のTSMCです[19][20]。TSMC創業者のモリス・チャン氏は当初利益を上げられるかどうか自信は無かったそうですが[19]、結果としてこのビジネスモデルは成功しました。GPU以外にもBroadcom、Qualcommなどに代表される通信用のチップなどの需要があったことと、プロセスが微細化するにつれ、工場の設備投資が莫大になって多くの企業が追従できないというのも成功の要因であったと思います。

日本の半導体メーカーもこのビジネスモデルに追従しましたが、やはりTSMCは技術は高く、高品質で高い世界シェアを誇っています。台湾の企業は電子機器の製造を受託するビジネスモデルのEDA (Electronic Design Automation)でも鴻海精密工業(日本のシャープが傘下に入り、経営危機を救われることとなった)等の活躍が目立ちます。

記事内容は平野先生HPより転載しております。

参考文献

- IEEE International Roadmap for Devices and Systems (IRDS)

- 半導体技術ロードマップ専門委員会

- 斎藤光男: 開発物語「プレイステーション2」用プロセッサ「Emotion Engine」, 電子情報通信学会通信ソサイエティマガジン(B-plus), Vol.5, No.4, pp.328-333, 2012.

- A.R. Smith, “The Real Story of Pixar,” IEEE Spectrum, Aug. 2021.

- “The High-k Solution”, IEEE Spectrum, Vol.44, No.10, pp.29 – 35, Oct. 2007.

- “Intel Transistors Enter the Third Dimension”, IEEE Spectrum, May 2011.

- “How the Father of FinFETs Helped Save Moore’s Law”, IEEE Spectrum, April 2020.

- “Intel: Back on Top by 2025?”, IEEE Spectrum, July 2021.

- “Intel’s Stacked Nanosheet Transistors Could Be the Next Step in Moore’s Law”, IEEE Spectrum, Dec. 2020.

- “Winner: The Ultimate Dielectric Is…Nothing IBM packs wires in vacuum to speed chips and save power”, IEEE Spectrum, Jan. 2008.

- “GlobalFoundries, Arm Close in on 3D Chip Integration”, IEEE Spectrum, Aug. 2019.

- “Next-Gen Chips Will Be Powered From Below”, IEEE Spectrum, Aug. 2021.

- “Morris Chang: Foundry Father”, IEEE Spectrum, Apr. 2011.

- “TSMC’s Morris Chang Says No to Apple, Qualcomm”, IEEE Spectrum, Aug. 2012.